Webinar Recording: DDR5 Post-Layout Verification: Find and Fix Causes of Failure

Comments

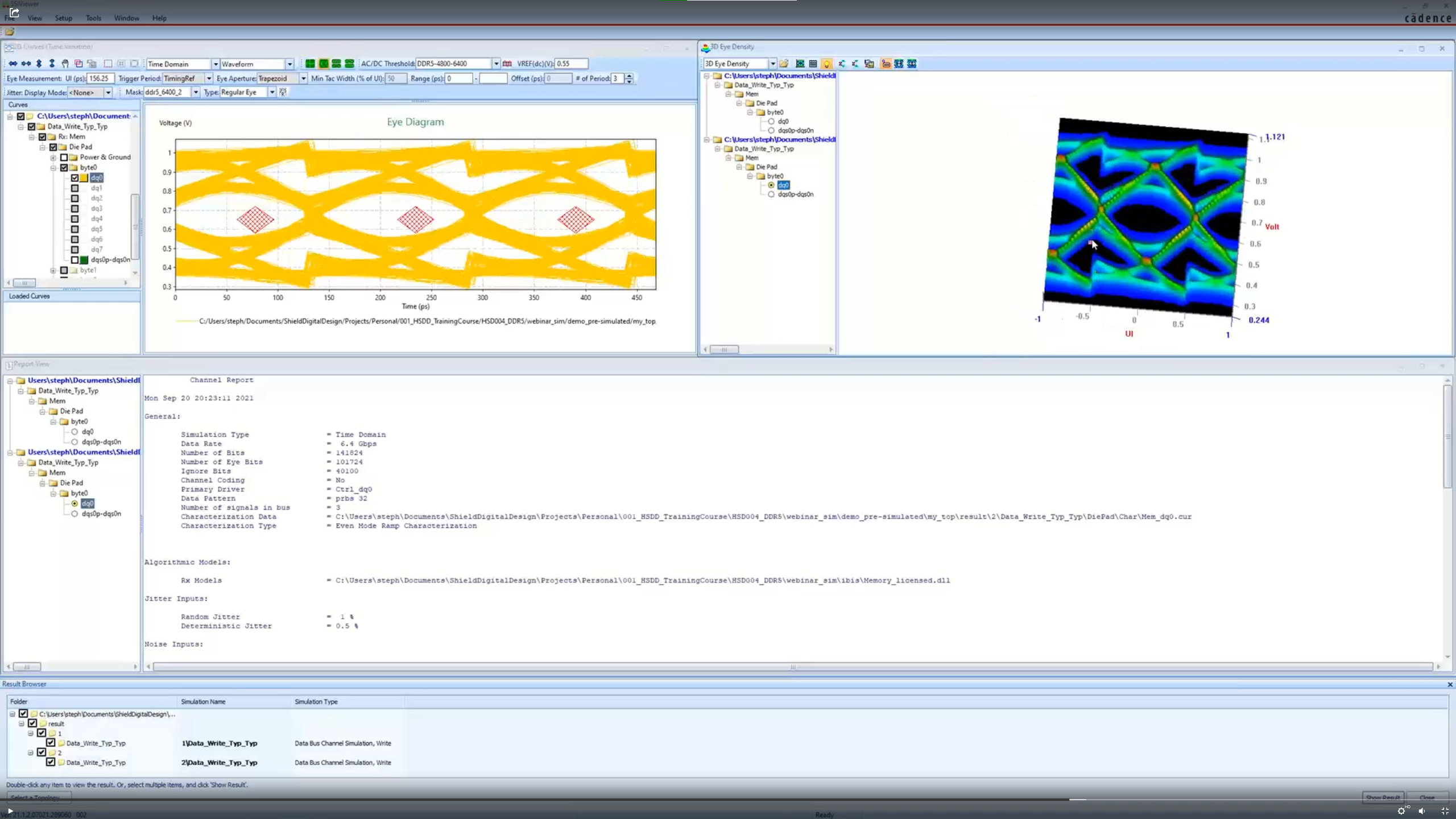

I recently presented (another) webinar with EMA Design Automation to discuss DDR5 ! This time the discussion was centered around a live post-layout demo. In the example, I showed the analysis of a board with PowerSI (which, of course, had some failures when the DDR report was generated). We then used S-parameter and TDR analysis to track down the failures. Lastly, we used the Clarity Via Wizard to generate new via models and we used Allegro High-Speed Structures to place them in the layout. Lastly, the board was verified to show a passing report.

DDR5 represents a significant performance improvement to the DDR interface over DDR4 with data transfer rates going from 3200 MT/s to as much as 8400 MT/s according to the JEDEC spec. With this increased performance comes architectural changes that must be understood to effectively design and leverage these next generation memory devices. These changes also require updated simulation techniques and methodologies to ensure accurate and effective characterization of the DDR5 interface.

The slides and recording are available at the EMA website, or watch the video below.

Table of Contents

Related Engineering Insights

Webinar Recording: A Dive into DDR5: An Engineers Guide to Simulating and Validating the Latest Generation of DDR

I recently presented a webinar with EMA Design Automation to discuss DDR5 …

Webinar Recording: 6 Common SI/PI Issues Lurking in Your Design And How to Prevent Them

I recently presented a webinar with EMA Design Automation to explain some …

Why Buy When You Can Spend More Time and Money Making Your Own?

We've all been there: you've got a problem to solve and are faced with the make …